Windows 10 is the newest member of windows NT family of which general availability was made on July 29, 2015. It is the successor of Windows 8.1. Windows 10 is supported on Intel Architecture 32 bit, AMD64 and ARMv7 processors.

As a Linux-user for more than 8 continuous years, I thought to test Windows 10, as it is making a lots of news these days. This article is a breakthrough of my observation. I will be seeing everything from the perspective of a Linux user so you may find it a bit biased towards Linux but with absolutely no false information.

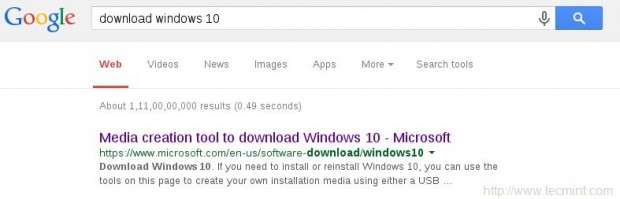

1. I searched Google with the text “download windows 10” and clicked the first link.

You may directly go to link : https://www.microsoft.com/en-us/software-download/windows10ISO

2. I was supposed to select a edition from ‘windows 10‘, ‘windows 10 KN‘, ‘windows 10 N‘ and ‘windows 10 single language‘.

For those who want to know details of different editions of Windows 10, here is the brief details of editions.

- Windows 10 – Contains everything offered by Microsoft for this OS.

- Windows 10N – This edition comes without Media-player.

- Windows 10KN – This edition comes without media playing capabilities.

- Windows 10 Single Language – Only one Language Pre-installed.

3. I selected the first option ‘Windows 10‘ and clicked ‘Confirm‘. Then I was supposed to select a product language. I choose ‘English‘.

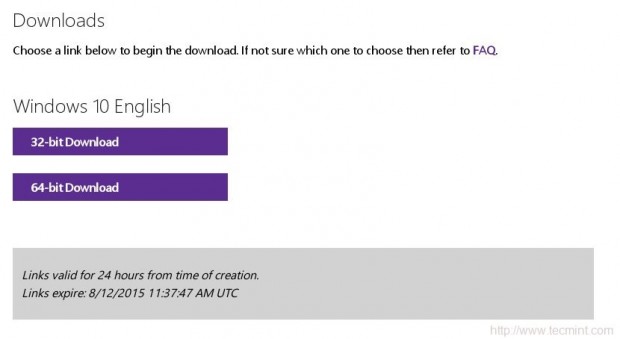

I was provided with Two Download Links. One for 32-bit and other for 64-bit. I clicked 64-bit, as per my architecture.

With my download speed (15Mbps), it took me 3 long hours to download it. Unfortunately there were no torrent file to download the OS, which could otherwise have made the overall process smooth. The OS iso image size is 3.8 GB.

I could not find an image of smaller size but again the truth is there don’t exist net-installer image like things for Windows. Also there is no way to calculate hash value after the iso image has been downloaded.

Wonder why so ignorance from windows on such issues. To verify if the iso is downloaded correctly I need to write the image to a disk or to a USB flash drive and then boot my system and keep my finger crossed till the setup is finished.

Lets start. I made my USB flash drive bootable with the windows 10 iso using dd command, as:

# dd if=/home/avi/Downloads/Win10_English_x64.iso of=/dev/sdb1 bs=512M; sync

It took a few minutes to complete the process. I then rebooted the system and choose to boot from USB flash Drive in my UEFI (BIOS) settings.

System Requirements

If you are upgrading

- Upgrade supported only from Windows 7 SP1 or Windows 8.1

If you are fresh Installing

- Processor: 1GHz or faster

- RAM : 1GB and Above(32-bit), 2GB and Above(64-bit)

- HDD: 16GB and Above(32-bit), 20GB and Above(64-bit)

- Graphic card: DirectX 9 or later + WDDM 1.0 Driver

Installation of Windows 10

1. Windows 10 boots. Yet again they changed the logo. Also no information on whats going on.

2. Selected Language to install, Time & currency format and keyboard & Input methods before clicking Next.

3. And then ‘Install Now‘ Menu.

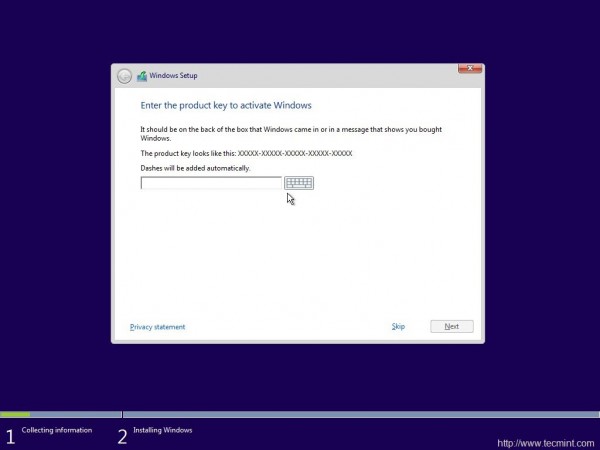

4. The next screen is asking for Product key. I clicked ‘skip’.

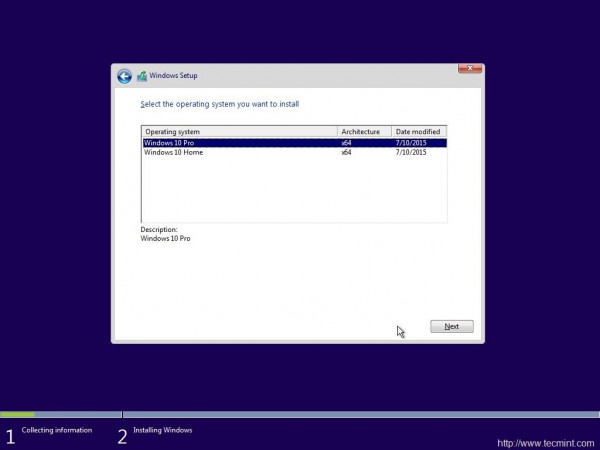

5. Choose from a listed OS. I chose ‘windows 10 pro‘.

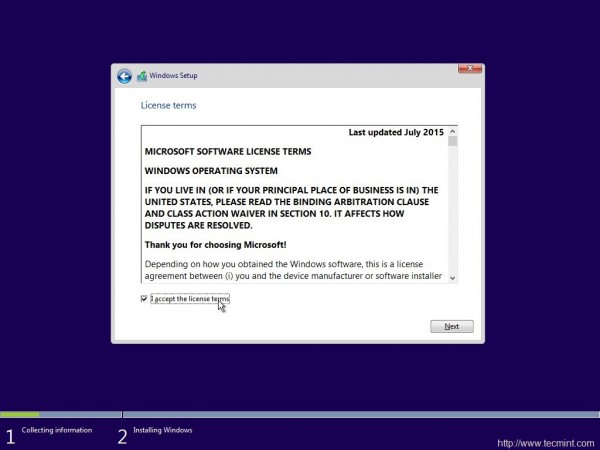

6. oh yes the license agreement. Put a check mark against ‘I accept the license terms‘ and click next.

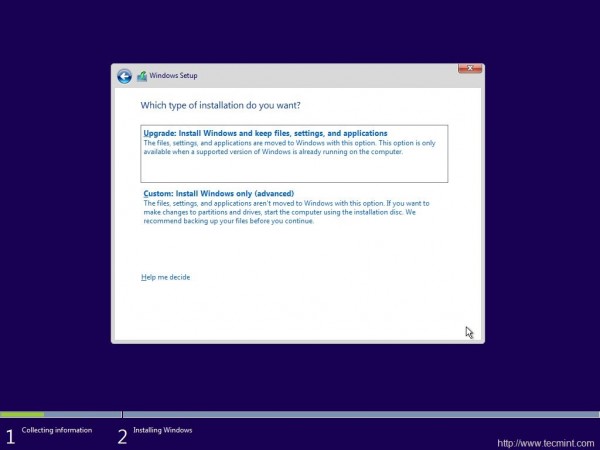

7. Next was to upgrade (to windows 10 from previous versions of windows) and Install Windows. Don’t know why custom: Windows Install only is suggested as advanced by windows. Anyway I chose to Install windows only.

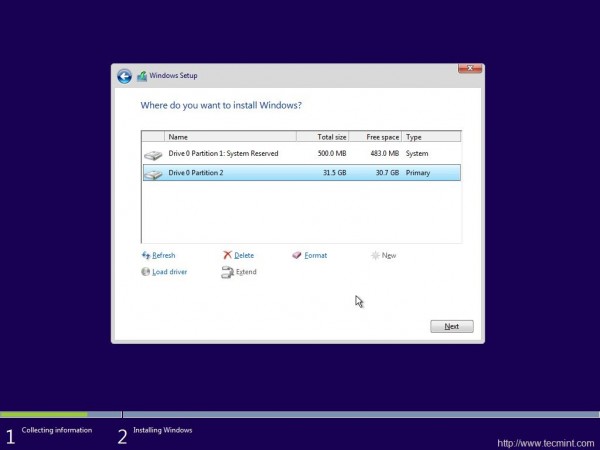

8. Selected the file-system and clicked ‘next’.

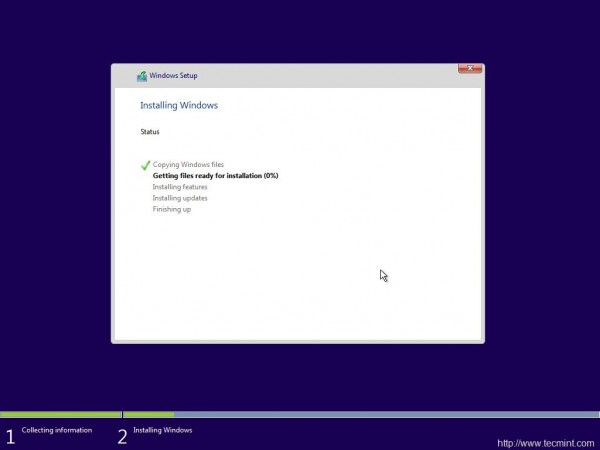

9. The installer started to copy files, getting files ready for installation, installing features, installing updates and finishing up. It would be better if the installer would have shown verbose output on the action is it taking.

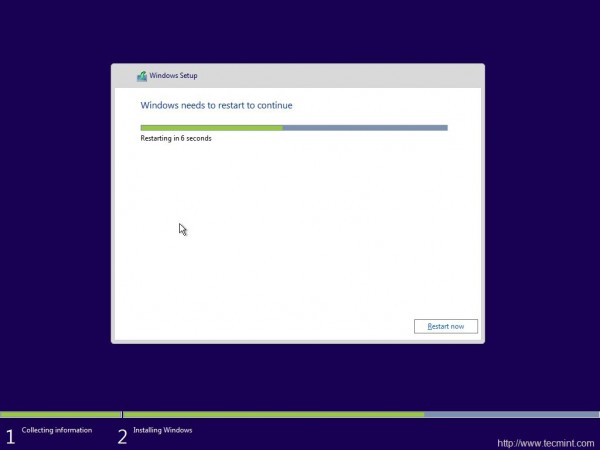

10. And then windows restarted. They said reboot was needed to continue.

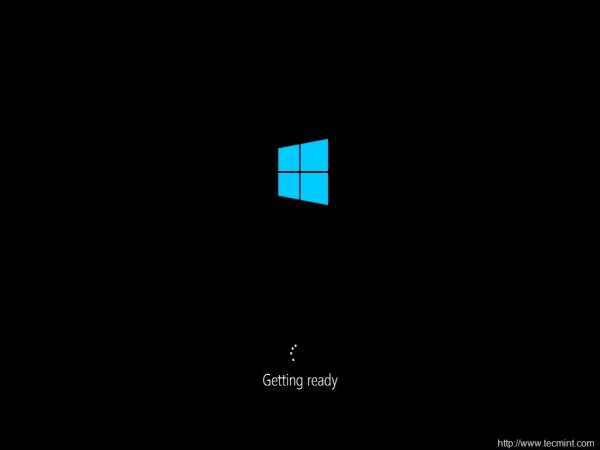

11. And then all I got was the below screen which reads “Getting Ready”. It took 5+ minutes at this point. No idea what was going on. No output.

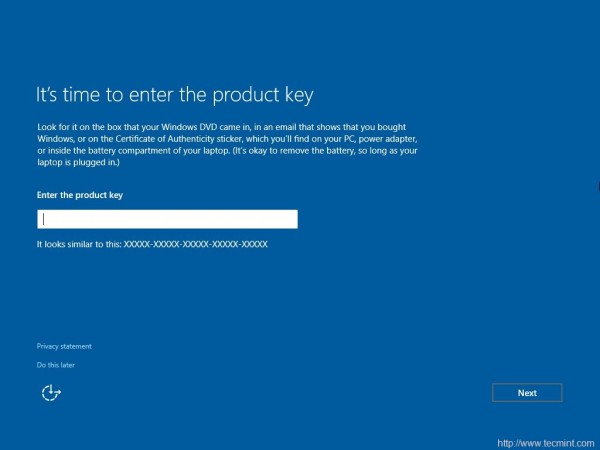

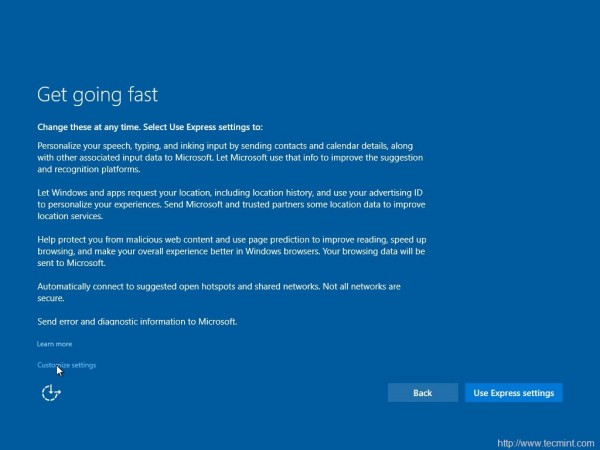

12. yet again, it was time to “Enter Product Key”. I clicked “Do this later” and then used expressed settings.

14. And then three more output screens, where I as a Linuxer expected that the Installer will tell me what it is doing but all in vain.

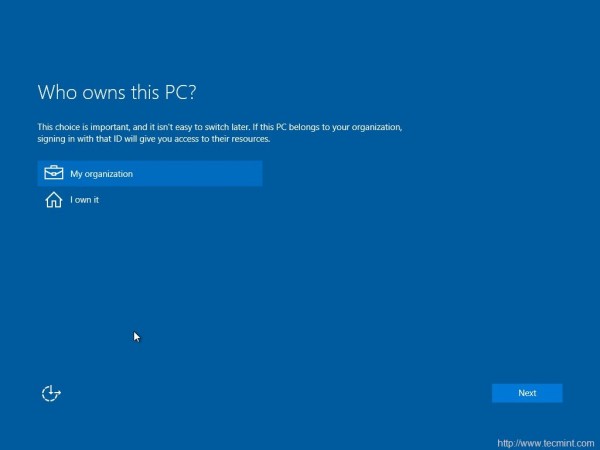

15. And then the installer wanted to know who owns this machine “My organization” or I myself. Chose “I own it” and then next.

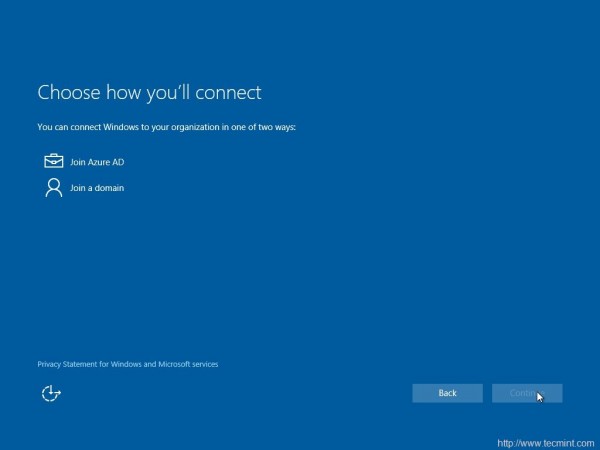

16. Installer prompted me to join “Azure Ad” or “Join a domain”, before I can click ‘continue’. I chooses the later option.

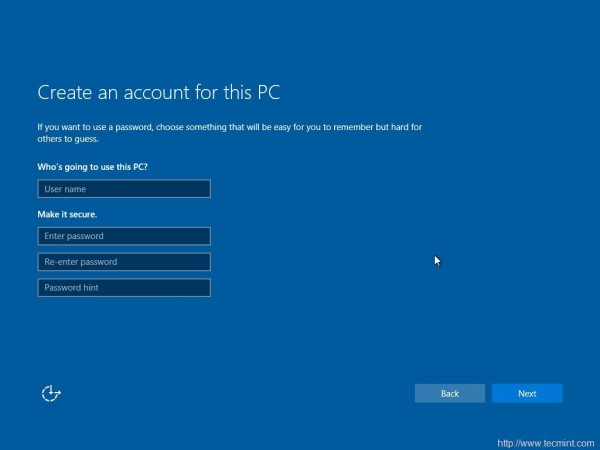

17. The Installer wants me to create an account. So I entered user_name and clicked ‘Next‘, I was expecting an error message that I must enter a password.

18. To my surprise Windows didn’t even showed warning/notification that I must create password. Such a negligence. Anyway I got my desktop.

For the part where you bash Windows for not asking for a password you don’t need a password to have a Windows account, thus, it did not release an error message. Frankly, it seems like you were just finding things to complain about, which normal users would not have even noticed.

how to install a trojan…. lol

The dd command seems wrong. It should have been of=/dev/sdb instead of of=/dev/sdb1.

I use both Windows 10 at work and Debian 8.5 at home. So let me share some observations with you guys.

1. Win 10 system requirements is a bullshit you need twice as much to run it smoothly. But the system is solid stable as hell.

A balanced net installation of Linux will work fine on 1Gigahertz CPU and 1 GB of RAM.

2. OK installation of Win10 is simpler then installation of Linux. No discussion.

3. Have no clue what was installed and how. Windows show me pictures.

4. Yes default win 10 Interface is beautifully clean and system boots relatively fast as long as you have more then 2 GB of ram and at least core duo CPU with more then 1MB on a first cache.

So in 99% of cases system act fine. In another case after it boots you must wait more then a minute until you can do anything besides enjoying the view.

By the way secret of lightning boot up is hiberfile.sys (that is probably created even when you totally turn of your PC). But I’m not sure of that.

5. Its jams your internet connection if you have cheap adsl you are screwed end of story.

6. You can not turn of updates they are obligatory and time consuming.

7. Updates aren’t consume your hd space. Updates replace files instead of adding files to existing ones. Well Linux has it since its beginning. But its a great improvement in Windows.

8. Drivers support is really awesome on Windows 10 its not a joke I was impressed.

9. MS EDGE Is blazing fast and stable I don’t know if its secure.

10. I cant compare Win 10 gui with my Linux desktop cause I use environment that is not so full of bells and whistles in compare of gnome or kde.

11. CLI package management that’s awesome news for sysadmins and advanced users.

12. It wants to send a bunch of stuff to MS see point 5.

You must take some effort to block its activity. Its an impossible task for normal user as our mom’s

13. As you said virtual desktop well we have it for 2 decades.

I feel like this review wasn’t done with an open mind.

There was no need to bash Windows over everything by comparing it to Linux. It’s just a matter of usecase, a particular features might not be useful for you but could be useful for another (type of) user and vice-versa.

Beside I have read about a few nice features which are not present in any of current Linux distros but Windows have it, like multi-touch trackpad with support for gestures, support for 4K display, etc but that side of the coin was ignored completely.

I feel the review could have been a little more unbiased, and the comparison at every single step could have been avoided.

PS: I’m a Linux user myself, the last time I owned a Windows machine was in 2010.

Linux does have support for gestures (I must admit maybe that it is worse than Windows’), but it has very good 4K display support.

I was unable to boot in to windows using dd command to make USB bootable ,is there any way to make my USB bootable.

@Rohit,

Use Unetbootin tool to create bootable USB drives as shown here

you could use winbot in Linux to create a live USB of any windows

do not get me wrong , i am a big Linux fan and i use it as my primary os of choice.

i strongly disagree ” with all respect” to the sentence “Linux is years ahead of Windows.”

basic functions does not work as it should compared to Mac / Windows , even latest builds for many applications that are cross platforms are not available by default or requires some work to do by the end user or wait for a 6 month spin of a new release to get it up and running.

Hi Avishek Kumar, I agree Linux is way ahead of Windows that is why they are copying certain features from Linux. I love Linux but at work I need to use windows because of Office, Outlook etc. I used Ubuntu 9.04 for 1 year 6 months no hassles until I got a new laptop where I worked at my previous company, anyway I want to move back to Linux (Mint 17.2 or Ubuntu but I need help to get Office, VPN client installed so that I can forget about Windows and only look through it at home lol) I saw an alternative of WINE for Linux called CROSSOVER you have to pay for it . Is there a good tutorial that you can help with for this kind of migration. You help will be much appreciated. If I get this to work then I will convince alot of users to move over to Linux.

Fernando Turner (South Africa)

Quite a few errors in this article, and you can really tell that the author is biased.

Nice article, but it should have gone through a basic revision.

I have been using Linux for over 11 years now, I have cut my teeth on using Fedora, Ubuntu, OpenSuSE, and Debian. I dropped Windows and their operating system since 2004, and after checking out Win10 I see nothing they’ve put out that would make me go back. I have been “virus-free” for over 11 years! That speaks volumes about the operating system I’m currently using (Fedora Linux) I won’t sit here and bash Microsoft, because you can see they’re making an effort to listen to their customers, but for me, I’m not inclined to download and use anything they have (except maybe for some kind of testing,)

Nice read.

Me too’ve trying it after 6-7 years of Mac.

It’s a good step ahead, we must give MS some credit here.

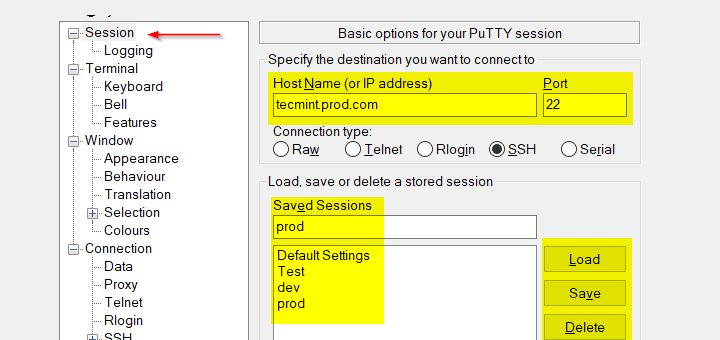

For me, the most surprising thing was how little has changed in the apps ecosystem. People keep talking about Mac vs PC in terms of hardware and OS. But not so much about apps. I could not believe it that 7 years later, the norm on windows are still Putty and Filezilla and Notepad++. And no good file manager whatsoever. Luckily there’s Atom now who can do a lot of things, although I wasn’t able to fully configure it (issues with node, python and compiling packages). Found a good terminal emulator though.

Didn’t know about OneGet – nice one. I found Chocolatey – like brew / apt-get / etc.

While I love Linux and use it day in day out on my servers and on my personal laptop I can honestly say from a business perspective Windows is still essential for the desktop.. Many of the apps we HAVE to run for legal requirements are only available on Windows and will not run under Wine. I don’t expect this to change any time soon either.

I have Windows 8.1 and I will not upgrade to 10 , I hate to see those tiles in windows 10 but now I only use it to shut down. What I like in an OS is Multimedia, multiprocessing, multithreading, low memory usage, speed, efficiency, and good privacy. The reason I still use Windows is that I want to see what programs I can download. What surprices me is I have not had any viruses yet. The problem is booting but I will solve it. I also like Linux but I have boot problems. 10 will be the last one and then bye bye M$. I hope Haiku Beta will be a success because it seems an OS for the future.

You had a boot Problem in Linux?

What distro you tried and which boot loader you installed?

I can help you on that part.

I find this article informative in-terms of comparison between Linux and Windows 10 . I’ve heard a lot about Windows 10 but I didn’t know what to expect from it.Am a full time Linux user for 6+ years, my Curiosity is now aroused to test out Windows 10 on my own.

Sure David Juma, test it and let me know what is your experience on Windows 10.

(Though deep down my heart i believe there is nothing to test in Windows 10 from a Linux Users Prespective.)

Those of you comparing software installation between Windows and Linux are forgetting the most crucial points to compare.

Besides the fact that package management is different from one distro to the next; Ubuntu is based on Debian which has their act together vs Ubuntu always botching their repos and upstream issues. Debian, Red Hat / CentOS, Arch, Suse… all have different managers so where the complaints are usually is Ubuntu and it’s forked derivatives.

Who here has even tried and compared Windows attempt at package management via the (chuckles) CLI yet?

I’m sure it isn’t anything like Linux for the same reason as my main point coming up next….

Windows Updates Windows and nothing else.

Linux updates EVERYTHING!

HOW & WHY?

Because all software is INCLUDED for free in Linux which is also Free.

FREE MY POINT?

Sure you can also find commercial software for Linux too but at least it all isn’t crammed down your throat as Trial bloatware that gets installed with Windows.

Oh sorry, you have to pay for that COA (which our author did not and won’t… up next Black Screen).

Oh and don’t forget to keep that wallet open because you’ll still have to pay for… Office, Anti-Virus, Money, and anything else that they threw in there that you want to use…. that is all free in Linux.

Yes I tried the CLI app installer – it sort of works on some but I tried to install ITunes that way – heh…. ITunes comes down as a zip file which, the installer informed me, was an empty compressed folder, can’t install. I had to take it on a mem stick to a Mint box and unzip it, take it back to windows box and then install the various bits.

There are lots of other wierdos, like the win box was connected to my network via a wifi dongle plugged in a front usb port. That was inconvenient so I moved it to a back port (this is a desktop machine) after which the network was inaccessible and could not be re-enabled until a re-boot. Plug and play?

I agree with the author re the lack of feedback during install – found that appalling. Not to mention the size of the downloads and updates. I blew over 16 GB on one install ( granted, I started from and insider preview copy) but 3.8 GB for a 64bit iso that supplied the OS and virtually nothing else. Come on.

Finally, if you are going to use this OS, be very aware of the liberties MS will take of your network bandwidth. Google windows 10 and feedback first.

Thanks for the feedback WilliamD,

Even I tried the CLI Package Manager. It stands no where as, compared to a Linux Package Manager. It seems to be a very immature project, but after all windows is all about it.

Hi, I’m also a Linux user(Ubuntu & Arch), and I totally agree with the report that you generated as per your experience with Windows’ latest installment. I think the whole Linux scenario has started to change now. With developers releasing AAA title of games on Linux, hardware manufacturers are also turning to support Linux users. The software quality on Linux has really improved and it’s UX/UI clearly rivals Windows’. The only thing that’s holding people back are some myths related to Linux and their resistance to change.

Well said Apurv,

Linux is becoming an OS of General users for general day-to-day work. With the availability of so many Linux Distributions and a huge community supporting each, we will see Linux ruling Personal computing and gaming market very soon.

Thanks for your feedback. Keep connected.

I have just upgraded from standalone windows 8.1 to windows 10 by using ms auto upgrade on lenovo G500 corei5 3rd gen.

1. I still face shutdown and booting issue. On my laptop, I had experienced blue screen error of death due to failure of power on/off driver. It persisted and annoyed me in windows 10 installation process.

2. Installation process took 07 hours. It required manual interruption to restart again by power button press after every reboot during installation process due to above mentioned flaw in driver.

3. After completion of installation, first I saw a message that please wait a while. Then I got message that it is taking longer than usual please wait.

4. My desktop loaded as slow as that of windows 8.1. No significant or even minute improvement in loading desktop icons and speedy opening of apps after logging in.

5. First thing I did was unpinning win appstore and then ms edge. Right click was not responsive and I achieved my objective after waiting 1/2 hour and getting my desktop responsive.

6. Start menu has improved than previous unresponsive metro. Still edge and some storeapp stuff were pinned there. So I had to unpin those.

7. First app I loaded was chrome. It loaded slow as usual. I opened page of facebook but it crashed in flash plugin in continuous 03 tries. Whereas diasp.org opened fast on first try. The default chrome browser page didn’t loaded completely.

8. File explorer looks like custom gnome icon theme. Default view is shifted to recent files.

10. I pressed the search button 10 times by now. Still hoping windows search will open and I will see something.

11. In short windows 10 is same old crap ware. Nothing new just copied features of gnome desktop which we are familiar from years.

12. It just gave me a psychological feeling of something new for few milliseconds just like that feel when you carwash and service and have feeling that your car got some salient feature.

13. My rating for win10 is 0/10.

[FR]

Ah! Windows, Never mind it is an old wine in new bottle everytime.

Well, i was lucky in a few prospective as compared to you.

My installation didn’t take so long time, neither anything crashed while testing. But overall there is nothing for a Linux-er.

It’s seriously weird to see a company with everything in their favor, still unable to release something stable that people can really use without getting into any kind of trouble.

Actually Windows and weird are synonymous words.

Interesting article. Of course, one area that Windows is light years ahead of Linux is software installation. I can’t recall the last time I couldn’t install software on Windows (double click setup.exe or an .msi installer and click “Next” repeatedly).

Linux? Even with package managers, installing software can be a real pain. “Sorry, you need lib-g.so.vx1.5 but you have 1.4 and can’t install 1.5”. Sound familiar? Oh right, the package installers don’t say “Sorry”, they just don’t install what you want. My bad.

Thanks for your feedback.

I agree that sometimes package installation in Linux is a pain. But if it is painful i know what is the issue and i have ways to fix it. Also, when removing a package i have the option to cleanly remove it. But if I were on Windows I won’t have ever know the reason why installing/not installing. Also no clean removal. No silly registry.

That’s not right. We’ve got “Ubuntu Software Center” and “Mint Software Center” that deal with exactly this kind of situations. And if you’ve got an offline .deb file, then gdebi takes care of dependencies. It’s really easy compared to windows. In windows, applications will install before checking the minimum requirements and after installation they’ll show you an error that this particular component is missing, a better example for that would be “.Net framework 2.0/3.0”. And it takes forever to install(at least in my case). And I don’t need to worry about application updates on Linux, cause they are delivered with system updates(and still I’m in control of what to install and what not to). And with Ubuntu’s snappy packaging, we won’t be having any kind of PPA or delayed update problem. The system will be more stable and the updates will also perform in a better way. I don’t see any reason why it’s so difficult for a Windows user to understand Linux? I had been using Windows for almost all my computer years(till Win7), and when I tried Linux Mint(which came bundled on a DVD with a tech magazine), I was able to understand everything. All of the required softwares in one place, organized nicely under a software manager!

Yup! Apurv,

Gone are the days when one not-so-techno-users fear Package Installation. The time has changed and so is the situation. Auto dependency resolution with yum, apt, dnf, yaourt, emerge has made the world a better place. If one still disagress (s)he is ignorant and Linux is not for Ignorant.

IE is still there in all programs as is the control panel. And you can see, block, hide what updates are pushed just like before.

IE means Internet explorer is still there in all programs?

I don’t know what you mean, but IE has been replaced by Microsoft Edge. And in my case the utility to block updates didn’t work. But no complaint! Windows has always remained this way all their life. Hope the legacy will continue.

Actually IE isbthere load edge top right menu.. load in internet explorer. Then when IE is loaded you right click on toolbat icon and pin it to menunar and voila.. Use IE instead of edge… why should you? EDGE is not really reconized by any web sites. .. and just for the record i am. Linux admini. But for home i use windows….. i enjoy Cod too much to give up windows… sorry guys.